寄生參數的深度剖析

一、寄生參數的內涵

寄生參數是在構建模型或系統時引入的附加參數,用于更精準地描述模型或系統的行為。雖與主要參數關聯性較弱,但對性能有不可忽視的影響。在電路領域,寄生參數的產生與設計、制造和布局等諸多環節緊密相連,對電路性能的發揮起著關鍵作用,因而成為電路設計與仿真過程中必須考量的因素。

二、MOS 管寄生參數的種類及其影響

MOS 管寄生參數是集成電路設計中除基本電氣特性外的額外參數,源于制造工藝、封裝形式及電路布局等多方面因素。深入探究 MOS 管寄生參數,可發現其包含以下幾種典型類型:

(一)輸入電容 Cgs

即柵極與源極間電容。當柵極信號波動時,因這二者間存在電容,易引發電壓延遲和相位延遲問題。在高頻電路設計語境下,精確構建輸入電容模型至關重要,關乎電路性能的穩定性與可靠性。通過嚴謹的數學建模和仿真分析,可對輸入電容的影響進行量化評估,從而采取針對性措施予以優化。

(二)輸出電容 Cgd

?指向漏極與柵極間電容。MOS 管運作過程中,該電容的存在致使輸出電壓變化延遲及相位延遲。對于高速數字電路而言,輸出電容模型的精準度直接關系到電路能否穩定、可靠運行。借助先進的測試手段和建模技術,能夠獲取高精度的輸出電容模型,為電路設計提供有力支撐。

(三)反向傳輸電容 Cgb

?為柵極與襯底(或基極)間電容。在 MOS 管工作時,它會導致電流反向傳輸及漏電流攀升。于低功耗電路設計中,準確建立反向傳輸電容模型是保障電路低功耗與高性能表現的關鍵所在。通過對反向傳輸電容的細致分析和建模,可優化電路的功耗特性,延長電池供電設備的續航時間。

(四)漏極電導 Gds

?描述漏極電流與漏極電壓間關系。MOS 管工作過程中,漏極電流與電壓的內在聯系使得漏極電流呈現非線性增長,漏極電壓也隨之非線性變化。在模擬電路設計領域,構建精準的漏極電導模型對于確保電路的線性與穩定特性意義重大。運用非線性電路分析方法和建模技術,可對漏極電導的影響進行有效補償,提升模擬電路的性能。

(五)柵極電導 Ggs

反映柵極電流與柵極電壓間關系。在 MOS 管工作狀態下,柵極電流與電壓間的關系導致柵極電流非線性上升,柵極電壓亦呈現非線性波動。對于模擬電路設計來說,精確的柵極電導模型是保障電路線性與穩定性的必備條件。借助微分方程建模和電路仿真技術,能夠深入揭示柵極電導對電路性能的影響機制,進而采取優化措施。

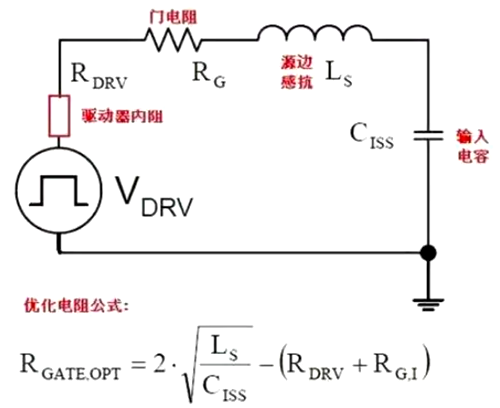

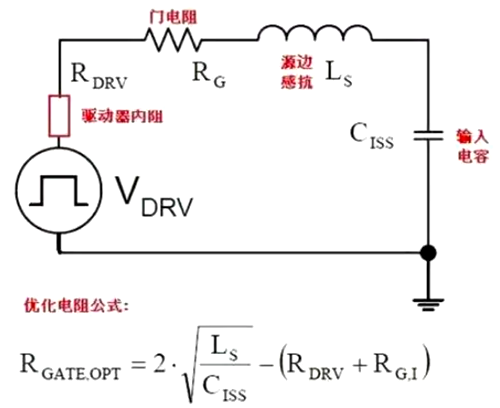

除上述寄生參數外,源邊感抗與漏極感抗也不容小覷。源邊感抗主要來自晶圓 DIE 和封裝間 Bonding 線的感抗,以及源邊引腳至地的 PCB 走線感抗;漏極感抗則由內部封裝電感及連接電感構成。

這些感抗因素在特定電路條件下,會對信號傳輸的完整性和電路的動態響應產生顯著影響。

這些感抗因素在特定電路條件下,會對信號傳輸的完整性和電路的動態響應產生顯著影響。

三、MOS 管寄生參數對電路性能的多維度影響

Cgs:在高頻電路設計中,若忽視 Cgs的影響,易引發信號傳輸延遲、反射等問題,降低電路的帶寬和穩定性。例如,在射頻放大器設計中,過大的 Cgs可能使放大器的高頻增益下降,甚至出現振蕩現象。通過采用共源共柵等電路拓撲結構,可有效減小 Cgs對電路性能的不利影響,提升高頻電路的穩定性和可靠性。

Cgd:對于高速數字電路,Cgd是導致數字信號邊沿失真、傳輸延遲的關鍵因素之一。在高速信號傳輸過程中,Cgd會使信號的上升時間和下降時間延長,降低數字電路的開關速度和數據傳輸速率。通過優化 MOS 管的版圖設計,減小柵極與漏極間的耦合面積,可降低 Cgd的值,進而提升數字電路的性能表現。

Cgb:在低功耗電路設計場景下,Cgb引起的電流反向傳輸和漏電流增加會顯著提升電路的靜態功耗和動態功耗。以微控制器(MCU)的待機模式為例,過大的 C

gb可能使 MCU 的待機功耗超標,縮短電池壽命。通過優化半導體制造工藝,降低襯底的摻雜濃度,可減小 Cgb的影響,實現低功耗電路設計目標。

Gds和 Ggs:在模擬電路設計領域,Gds和 Ggs的非線性特性會破壞電路的線性傳輸特性,導致信號失真、增益波動等問題。例如,在模擬濾波器設計中,若不考慮 Gds和 Ggs的影響,會使濾波器的幅頻特性和相頻特性偏離設計預期,影響信號的濾波效果。通過采用線性化設計技術,如源極負反饋等,可抑制 Gds和 Ggs的非線性影響,提高模擬電路的線性和穩定性。

四、過孔寄生參數及其量化計算

在高速數字電路設計領域,過孔作為連接各層印制導線的關鍵結構,除了實現電氣連接功能外,還會產生寄生電容和寄生電感。這些寄生參數在高頻信號傳輸過程中,會對信號完整性造成嚴重破壞,如引發信號反射、串擾等問題。

寄生電容的計算公式為 C=1.41∈TD1/(D2-D1),其中,C 表示過孔寄生電容,ε 為 PCB 板基材的介電常數,T 是 PCB 板厚度,D1是過孔焊盤直徑,D2是過孔在鋪地層上的隔離孔直徑。寄生電感的計算公式為 L=5.08h[ln(4h/d)+1],其中,L 是過孔寄生電感,h 為過孔長度,d 是中心鉆孔直徑。借助這些公式,可在電路設計前期對過孔寄生參數進行初步估算,為優化 PCB 布局布線提供理論依據。

五、寄生參數提取的標準化流程

在大規模集成電路設計中,寄生參數提取是確保電路設計精度的關鍵環節,其標準化流程如下:

(一)布局布線

依據工藝特性及參數要求,開展布局布線工作。這一階段需綜合考慮電路的電氣性能、布線密度、信號完整性等多方面因素,為后續版圖設計和寄生參數提取奠定基礎。通過運用先進的電子設計自動化(EDA)工具,結合設計團隊豐富的實踐經驗,可實現高效、合理的布局布線方案。

(二)版圖設計

基于布局布線結果,進行版圖信息文件的設計。版圖設計需嚴格遵循工藝設計規則,確保電路在半導體制造過程中的可行性。同時,要充分考慮寄生參數的影響,通過優化版圖的幾何形狀、布線寬度、間距等參數,降低寄生參數對電路性能的不利影響。版圖設計的質量直接關系到寄生參數提取的準確性和電路的最終性能表現。

(三)參數提取

運用計算機輔助設計(CAD)工具,對版圖進行寄生參數提取。CAD 工具通過復雜的算法和模型,對版圖中的各種幾何結構和物理特性進行分析,提取出線上電阻、電容以及寄生電阻電容等寄生參數,并生成網表文件。這些網表文件可用于布局與原理圖(LVS)檢查,驗證版圖與原理圖的一致性;也可用于后仿真,將寄生參數納入電路仿真模型中,更準確地評估電路的實際性能。通過與電路設計工程師的緊密協作,對提取的寄生參數進行驗證和優化,可不斷提升寄生參數提取的精度和可靠性,助力集成電路設計性能的持續提升。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280